到手拿到开发板,可以看到有俩个地方没有上料

如图

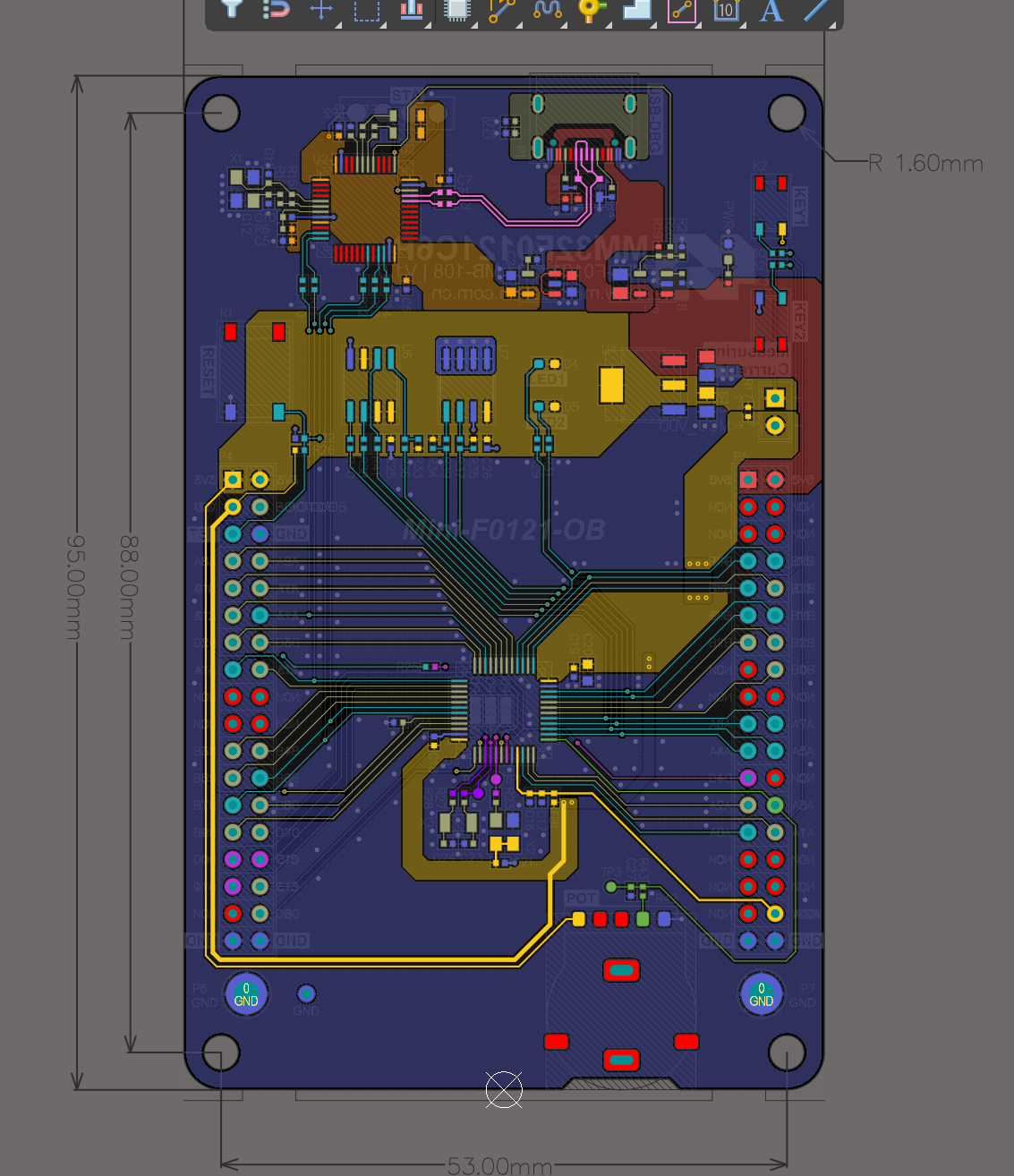

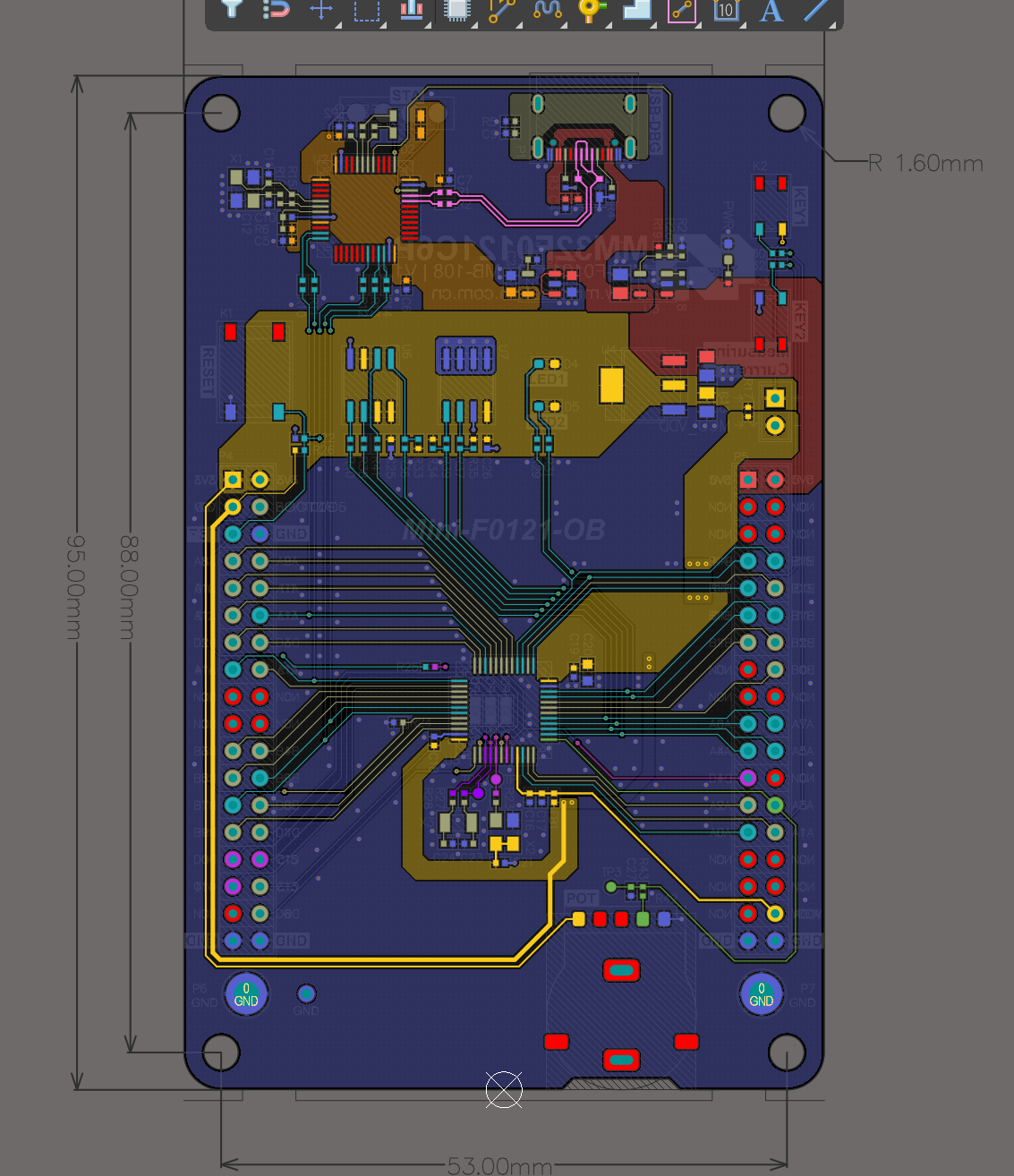

这里补一张pcb图 我觉得超级好看

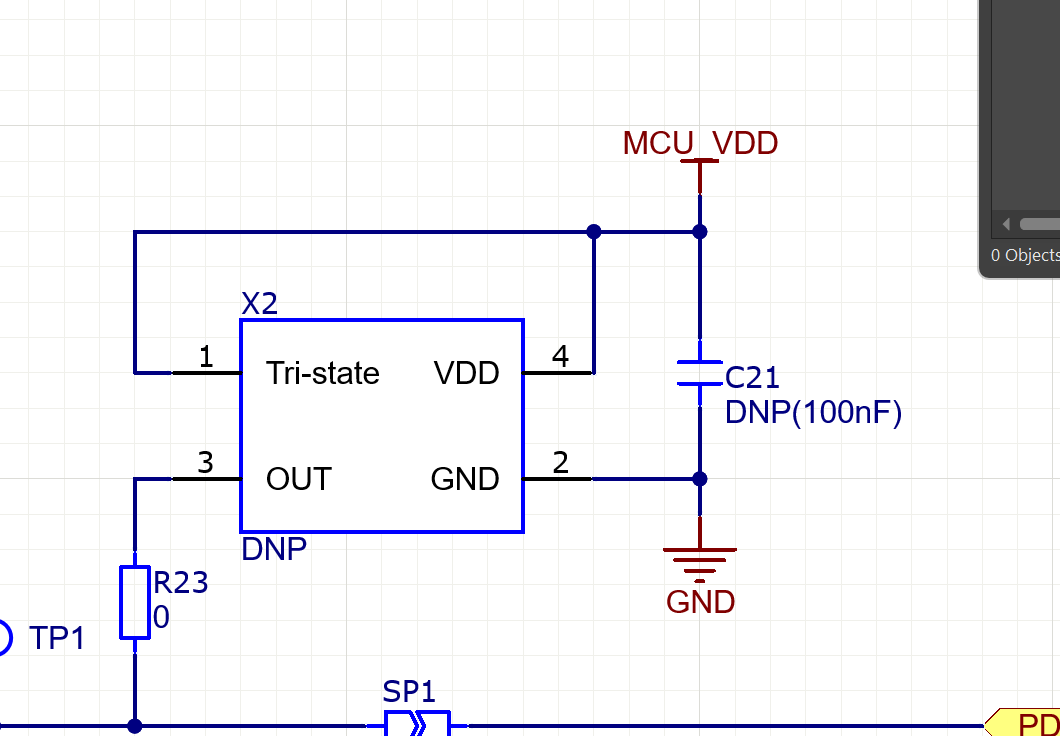

缺的是一个有源晶振 和一个100nf的电容

有源晶振可以上电就输出波形 ,不需要CPU的内部振荡器,信号稳定,质量较好,而且连接方式比较简单

这里我淘宝直接买了一个8m的晶振进行安装

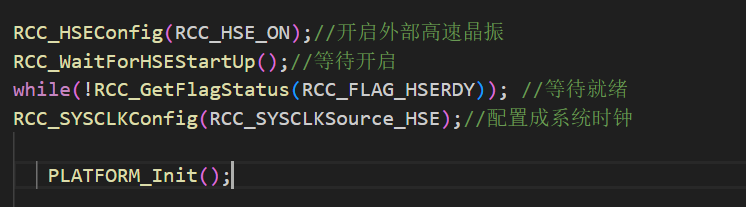

以下是 启用外部高速晶振的代码

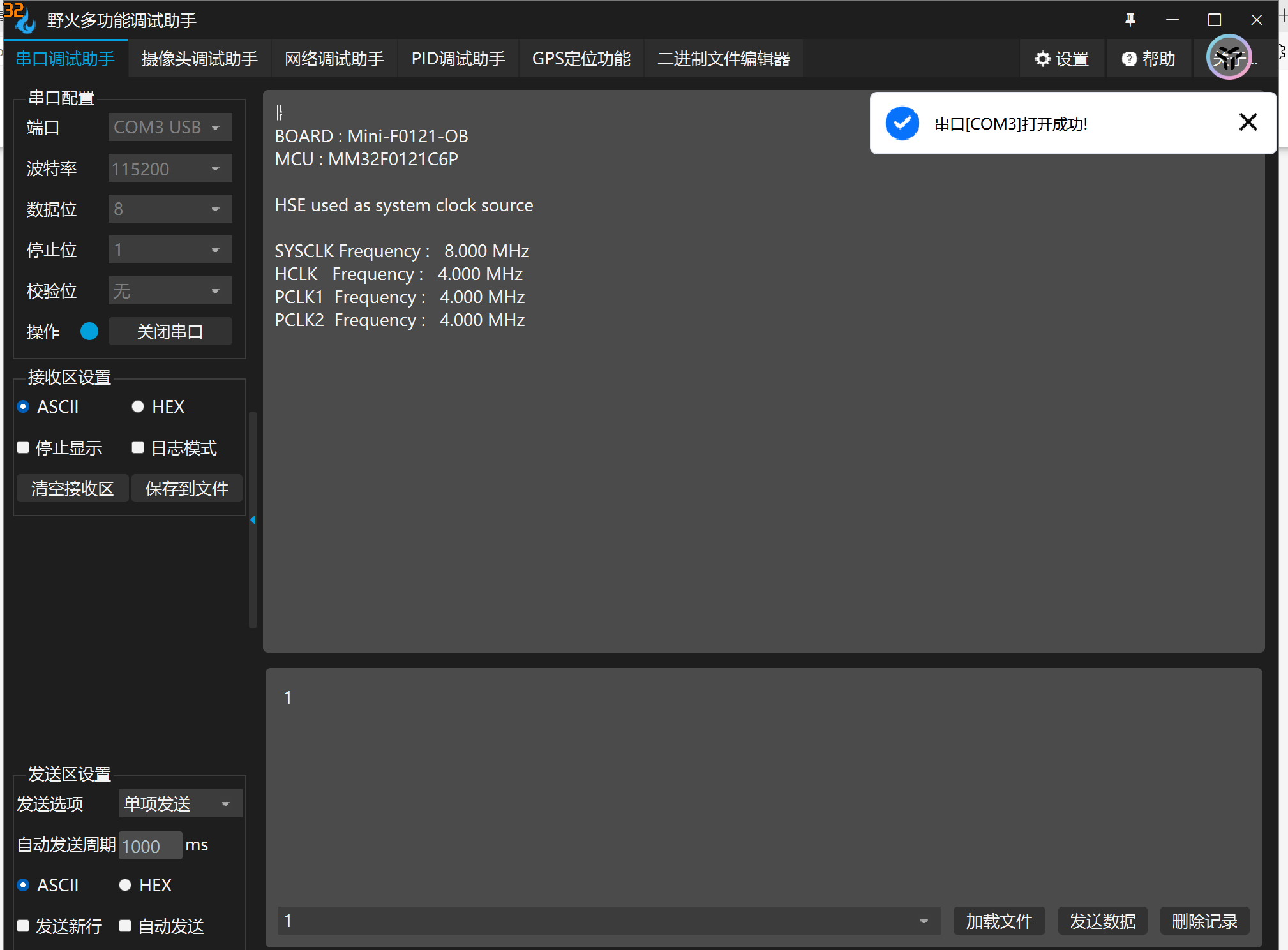

输出效果如图

但是只有8m那怎么办呢 ?

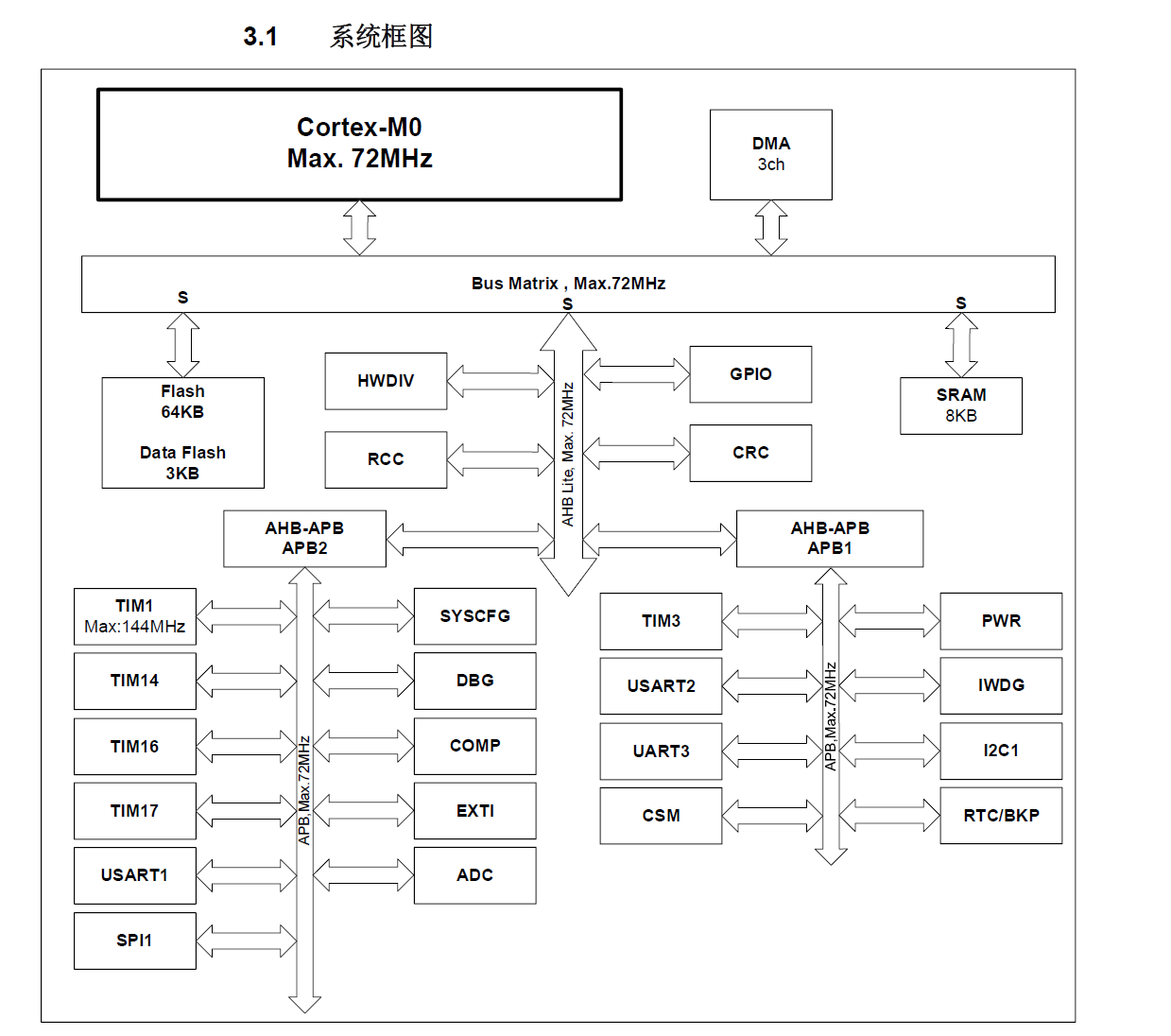

这里补一张系统框图可以看到外设在哪个总线下面

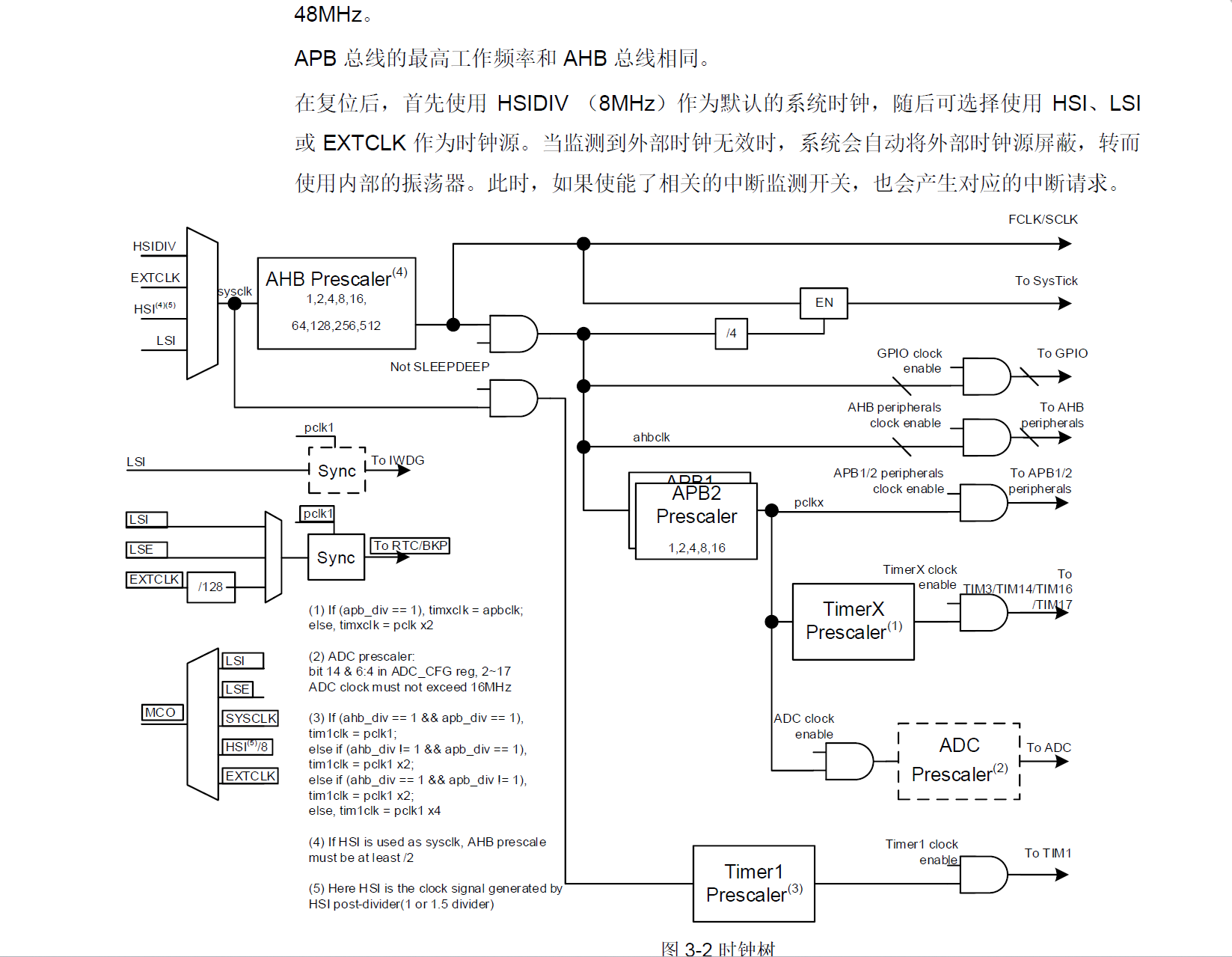

可以看到 外部高速晶振输入是EXTCLK

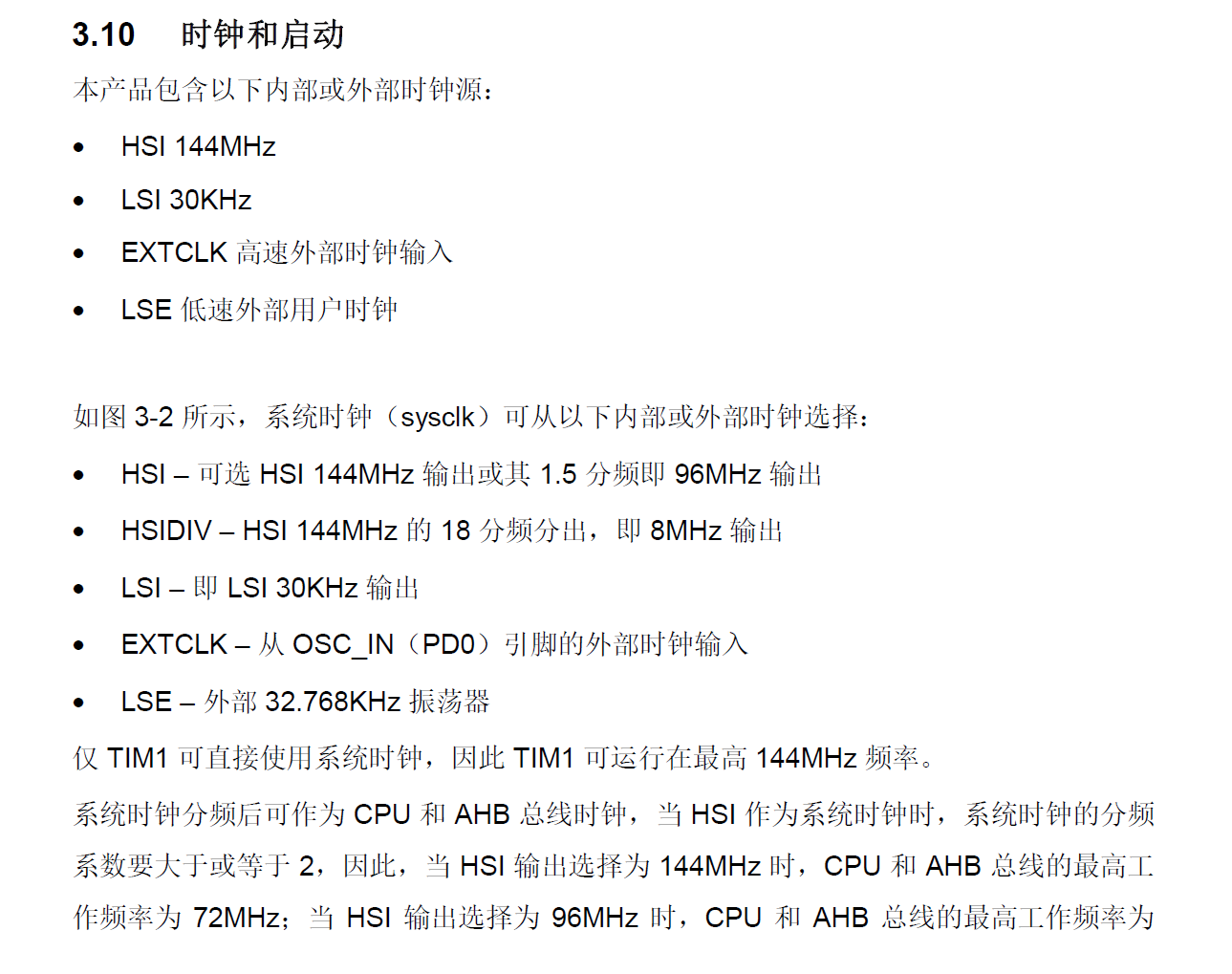

首先使用 HSIDIV (8MHz)作为默认的系统时钟,随后可选择使用 HSI、LSI

或 EXTCLK 作为时钟源。当监测到外部时钟无效时,系统会自动将外部时钟源屏蔽,转而

使用内部的振荡器

这是时钟系统的初始化流程

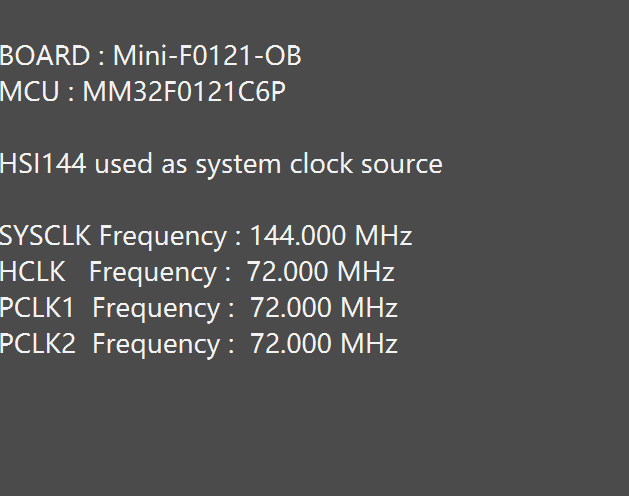

但是你如果不去调用启动外部晶振函数的话它是默认内部高速 也就是 144mhz

如图

这里可以看见 这里hclk对应ahb总线

pclk对应apb1

pclk2对apb2

但是内部没有倍频器 和pll锁相环 所以无法 将外部高速晶振时钟给他倍频上去

只能8m

大家还是用内部吧

开源社区

开源社区